au sommaire

Chaque cœur se compose d'une structure légère (170 millions de transistors) et d'une mémoire de 1 Mo un peu particulière. De type NUCA (non-uniform cache access), elle est composée de 16 blocs de 64 ko pouvant chacun être utilisé soit comme mémoi

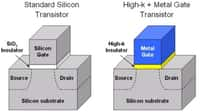

D'après Stephen Keckler, Doug Burger et Kathryn McKinley, de l'université d'Austin (Texas), les concepteurs de processeurs sont aujourd'hui dans une impasse. Après avoir élaboré des circuits de plus en plus complexes - les Cisc, Complex Instruction Set Computer - puis cherché à en simplifier la structure - les Risc Reduced Instruction Set Computer - avant de réaliser une hybridationhybridation de ces deux principes, les ingénieurs ont poussé dans ses retranchements la fréquence de l'horloge et n'ont désormais plus d'autres ressources que de multiplier les cœurs à l'intérieur d'un même boîtier. En restant dans ces ornières techniques, il ne resterait plus qu'un peu de puissance supplémentaire à grappiller.

Sous ce boîtier, deux cœurs seulement... mais une architecture révolutionnaire.

© Department of Computer Sciences / University of Texas at Austin

En 2003, cette équipe est partie défricher une voie nouvelle, touchant à la fois au matériel et au logiciel. Dans leur architecture baptisée Edge (Explicit Data Graph Execution)), le processeur n'exécute pas les instructions dans l'ordre dans lequel elles sont écrites dans le programme. Quel qu'en soit l'emplacement, elles sont exécutées dès que le calcul est possible, c'est-à-dire quand les résultats intermédiaires ont été obtenus. Par exemple, si un calcul établit la valeur de X, le processeur effectue immédiatement tous les autres calculs qui dépendent de la valeur de X. Pour parvenir à un tel fonctionnement, il faut qu'un compilateur examine le programme, du moins un grand morceau (appelé bloc), et établisse les interdépendances entre les opérations programmées en différents endroits. Le résultat de cette première analyse est un graphe, d'où l'appellation Explicit Data Graph Execution.

2048 instructions sous surveillance permanente

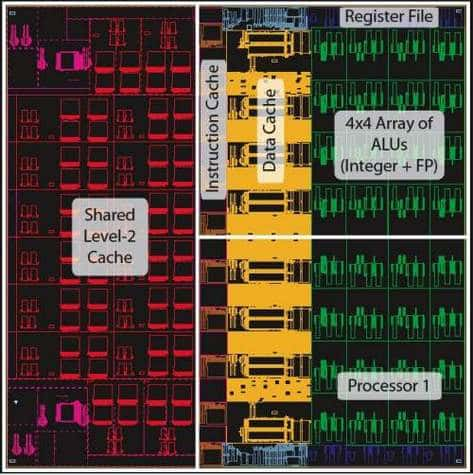

Associée à IBMIBM, l'équipe a réalisé un prototype, baptisé Trips (Tera-op, Reliable, Intelligently adaptive Processing System), car l'espoir est d'atteindre le teraflops, soit un millier de milliards d'opérations en virgule flottante par seconde (flops signifie floating point operations per second). Pour le construire, les chercheurs ont conçu une construction modulaireconstruction modulaire, qu'il serait facile d'utiliser pour réaliser un processeur bien plus puissant. Ce premier Trips contient deux cœurs, chacun pouvant exécuter seize instructions par cycle d'horloge. Conformément au principe de Edge, Trips surveille un ensemble d'instructions du programme pour les exécuter dès que possible. Chaque cœur s'occupe ainsi de huit blocs de 128 instructions, soit 1024 instructions par cœur susceptibles d'être exécutées à tout moment.

L'architecture de ce processeur acceptant jusqu'à 32 cœurs, l'équipe nous promet une puissance de 500 gigaflops accessible rapidement. En poussant plus loin le curseur de la prédiction, elle espère le téraflops pour 2012. Chez Intel, on nous le promet sur nos micros en 2029. Edge permettra-t-il d'y parvenir avant ?