Dans le cadre de l’International Solid-State Circuits Conference qui se déroule à San Francisco, des chercheurs de Stanford ont dévoilé le prototype d'un ordinateur qui tient sur un seul et même composant.

au sommaire

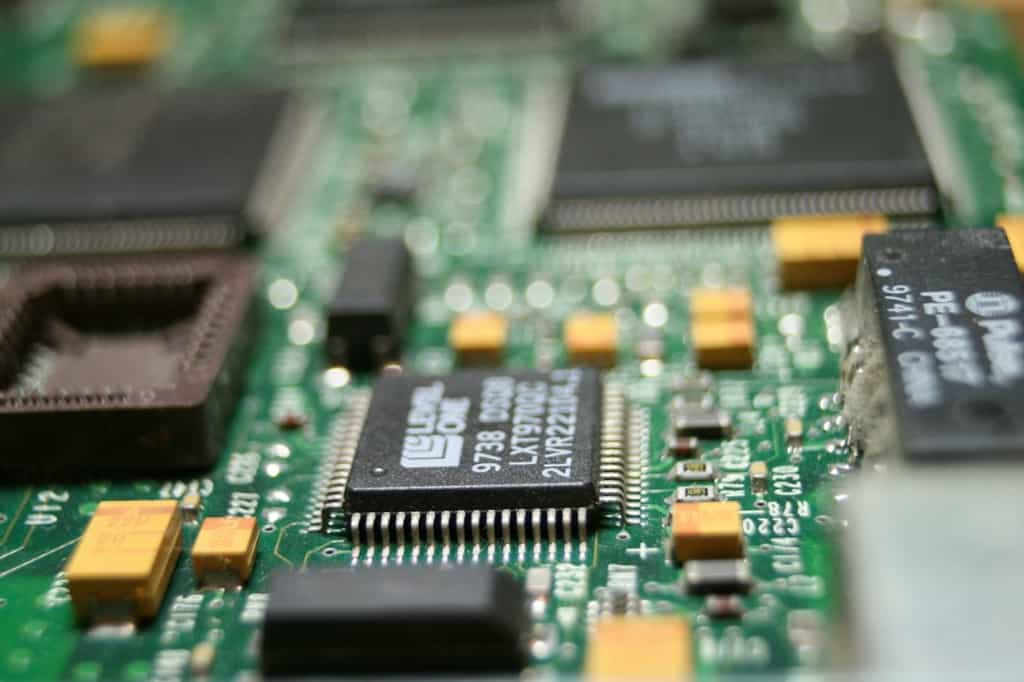

La miniaturisation a permis de nombreuses évolutions technologiques, comme les smartphones et les PC portables. Certains veulent pousser cette tendance encore plus loin, pour créer un ordinateur tellement petit qu'il pourrait être intégré à n'importe quel équipement. Dans ce but, une équipe menée par des chercheurs de l'université de Stanford aux États-Unis vient de dévoiler le prototype d'un ordinateur complet sur une seule puce électronique. Cette innovation a été présentée lors de l'International Solid-State Circuits Conference à San Francisco ce 19 février, un forum dédié à l'électronique.

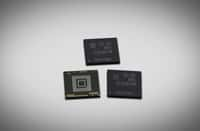

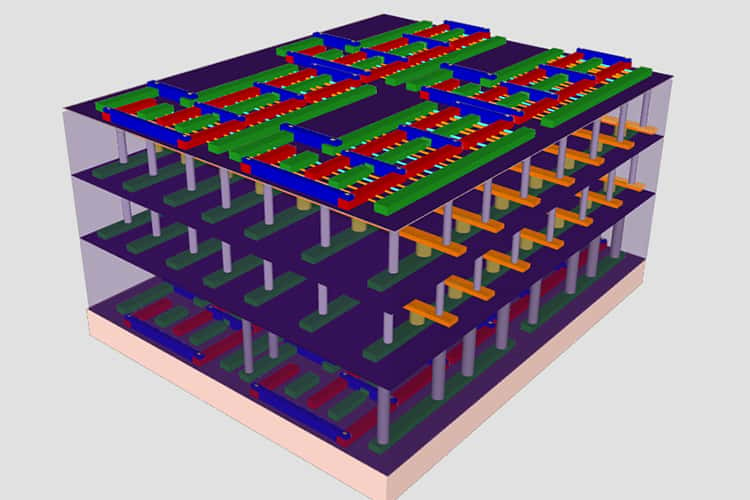

Concrètement, il s'agit d'un processeur surmonté d'une mémoire, utilisant une nouvelle technologie. Les chercheurs de Stanford se sont associés avec des scientifiques du Laboratoire d'électronique et de technologie de l'information (Leti)) de Grenoble pour développer cette mémoire et l'intégrer sur le processeur. Selon Subhasish Mitra, professeur d'ingénierie électrique et de sciences informatiques à Stanford, il s'agit de créer un « tout » plutôt « que la somme des parties ».

Une nouvelle technologie de mémoire

Ces ingénieurs ont développé une mémoire de type RRAMRRAM (resistive random-access memory) qui offre plusieurs avantages. Tout d'abord, il s'agit d'une mémoire non volatile, ce qui signifie qu'elle retient les données, même lorsque la puce passe en veille prolongée afin d'économiser l'énergieénergie. De plus, elle permet une densité de stockage plus élevée afin d'en réduire la taille, les chercheurs étant parvenus à augmenter la capacité de stockage de chaque cellule. Plutôt que d'enregistrer deux états, un 0 ou un 1, comme la grande majorité des technologies de mémoire informatique, chaque cellule peut stocker cinq états différents.

La mémoire RRAM offre une consommation électrique réduite ; l'intégration directement sur le processeur permet de réaliser encore plus d'économies. La réduction au minimum des circuits entre les deux éléments permet d'éliminer les pertes électriques et de réduire au maximum le temps de réponse, pour améliorer l'autonomie et la puissance du système. La mémoire et le processeur ont une consommation électrique qui équivaut à 1/10e de ce que consomment d'autres appareils équivalents, tout en gardant une puissance de calcul avancée. Ils ont ajouté un algorithme pour mieux gérer l'usure de la mémoire et affirment qu'elle dispose d'une duréedurée de vie d'environ dix ans.

Une technologie qui pourrait rapidement intégrer les smartphones

Le prototype ferait « le diamètre d'une gomme de crayon », soit six millimètres seulement. Le développement a nécessité la collaboration d'informaticiens et d'ingénieurs électriques, qui y ont intégré de nombreuses technologies matérielles et logicielles. Ce prototype serait encore trop grand pour certains développements du futur, comme avec l'internet des objets, mais le principe de combinaison de la mémoire et du processeur pourrait déjà être intégré dans de nombreux appareils. Cette nouvelle architecture intéresse déjà les fabricants de puces et pourrait permettre de nouvelles évolutions dans les smartphones et autres appareils mobiles.

Ce qu’il faut

retenir

- Des chercheurs de Stanford associés à des scientifiques du Leti de Grenoble ont développé un prototype de PC complet de la surface d'une gomme de crayon.

- La mémoire est intégrée dans le processeur.

- Cette puce d'un nouveau genre pourrait équiper les prochains smartphones.