Loin d’atteindre un seuil limite, la miniaturisation des microprocesseurs, ainsi que l’augmentation de puissance qui en découle, pourrait se voir relancée grâce à un nouveau procédé de gravure faisant appel à la troisième dimension.

au sommaire

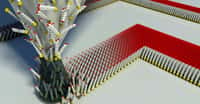

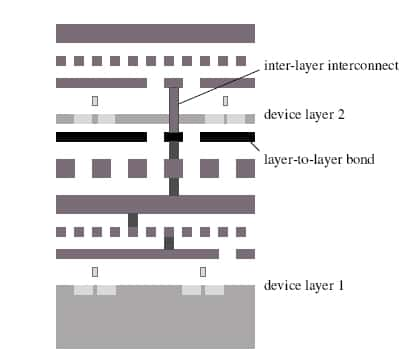

Schéma des connexions entre deux couches (layer 1 et layer 2), séparées par un isolant (bande noire). Crédit MIT

Jusqu'ici, les microprocesseurs évoluaient en puissance grâce à l'augmentation du nombre de leurs composants en suivant la loi de Moore, prédisant que leur nombre devrait doubler tous les deux ans. La prévision est remarquable puisque la période moyenne pour ce doublement a finalement été de 1,96 an entre 1971 et 2001. A noter au passage que l'énoncé d'un « doublement tous les 18 mois », que l'on rencontre souvent, est faux et ne figurait pas dans la citation originelle...

Au gré de la miniaturisation des composants et de la multiplication des cœurs sur une même galette de siliciumsilicium, cette montée en puissance se poursuit toujours. Mais la propagation de l'information le long d'interconnexions de plus en plus longues sur une surface toujours accrue pose problème. Et bien que cette solution présente des avantages sur le plan de la dissipation thermique, elle comporte ses propres limites : à quoi bon grimper en puissance si le temps de réponse doit s'allonger ?

Une voie différente semble logique : au lieu de juxtaposer les différents composants d'un circuit intégré, pourquoi ne pas les superposer ?

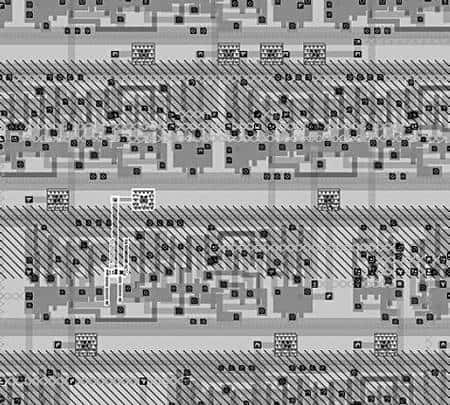

Schéma (fragmentaire) de la puce réalisée par Friedman. Partie inférieure. Crédit MIT

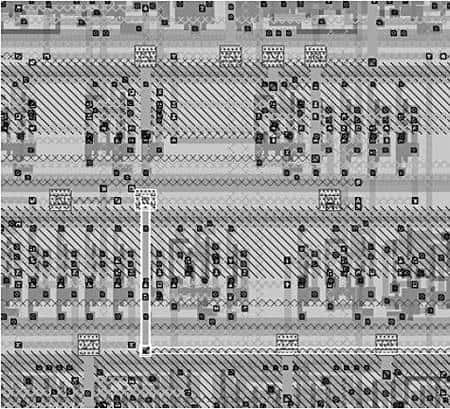

Partie supérieure de la même section, montrant les points de connexion. Crédit MIT

La gravure en trois dimensions

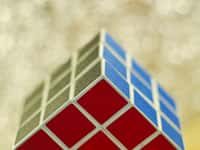

C'est dans cette optique que le professeur Eby G. Friedman, de l'université de Rochester, vient de réaliser le premier véritable processeur en 3D, baptisé le Rochester Cube. Des prototypes similaires avaient déjà vu le jour, mais les différentes couches qui les composaient n'étaient reliées entre elles que par quelques ponts d'entrées et sorties. Le modèle de Friedman, lui, comporte plusieurs millions d'interconnexions, tant sur le plan horizontal que vertical. Pour cette raison, le chercheur préfère parler de cube plutôt que de puce.

Réalisé avec l'aide du MIT (Massachusetts Institute of Technology)), le premier processeur fabriqué selon cette technologie est cadencé à une fréquence de 1,4 GHz. Mais il ne s'agit que d'un premier prototype, et selon Friedman, il serait aisé de réduire sa taille d'un facteur dix tout en multipliant sa fréquence d'autant.

Bien que cette nouvelle technologie soit encore embryonnaire et que sa commercialisation ne soit pas encore évoquée, elle semble déjà ravir la place de la mémoire holographique, prometteuse mais encore trop complexe, au panthéon des grands espoirs de demain. Selon Eby G. Friedman, « les puces superposées les unes aux autres peuvent réaliser des choses qui n'auraient jamais été faisables en 2D classique ».